#### ICP6000(X)/ICP9000(X) Hardware Description and Theory of Operation

DC 900-0408E

Simpact, Inc. 9210 Sky Park Court San Diego, CA 92123 January 1998

<u>**S**IMPACT</u>

Simpact, Inc. 9210 Sky Park Court San Diego, CA 92123 (619) 565-1865

ICP6000(X)/ICP9000(X) Hardware Description and Theory of Operation © 1989–1998 Simpact, Inc. All rights reserved Printed in the United States of America

This document can change without notice. Simpact, Inc. accepts no liability for any errors this document might contain.

Sun-3, Sun-4, and SunOS are trademarks of Sun Microsystems Incorporated.

## Contents

| Preface                                                       |           |

|---------------------------------------------------------------|-----------|

| 1 Overview of the ICP                                         | 17        |

| 1.1 Purpose of the ICP                                        | 17        |

| 1.2 ICP Applications                                          | 18        |

| 2 Unpacking and Configuration                                 | 21        |

| 2.1 Antistatic Precautions                                    | 21        |

| 2.2 Unpacking the ICP                                         | 22        |

| 2.3 Initial Inspection                                        | 22        |

| 2.4 Configuration                                             | 22        |

| 2.5 Jumper Options                                            | 23        |

| 2.5.1 U39 (ICP6000/ICP9000) Pinout Configurations             | 23        |

| 2.5.2 U7 (ICP6000X/ICP9000X) Pinout Configurations.           | 24        |

| 2.5.3 U19 (ICP6000/ICP9000) Pinout Configurations             | 25        |

| 2.5.4 U8 (ICP6000X/ICP9000X) Pinout Configurations            | <b>26</b> |

| 2.6 Software Programmable Configuration Options               | <b>28</b> |

| 2.6.1 Configuring the Slave Address Decoder                   | <b>28</b> |

| 2.6.1.1 Boot Flags                                            | 29        |

| 2.6.1.2 Slave Address Compare                                 | <b>29</b> |

| 2.6.1.3 Mode Selection                                        | <b>30</b> |

| 2.6.1.4 Slave Address Modifier Compare                        | 31        |

| 2.6.1.5 Slave Address Modifier Compare Don't Care             | 31        |

| 2.6.2 Configuring the VMEbus Master Interface and Interrupter | 32        |

| 3 VMEbus Installation                           | 35        |

|-------------------------------------------------|-----------|

| 4 Hardware Specifications                       | <b>45</b> |

| 4.1 Mechanical and Environmental Specifications | 45        |

| 4.1.1 Physical Characteristics                  | 45        |

| 4.1.2 Power Requirements                        | 45        |

| 4.1.3 Environment                               | <b>46</b> |

| 4.2 Device Specifications                       | <b>46</b> |

| 5 Hardware Overview                             | <b>49</b> |

| 5.1 Internal Architecture                       | <b>49</b> |

| 5.2 Microprocessor.                             | <b>49</b> |

| 5.3 Main Memory                                 | 55        |

| 5.4 PROM                                        | 55        |

| 5.5 Timers                                      | <b>56</b> |

| 5.6 Console Port                                | <b>56</b> |

| 5.7 Communications Devices                      | <b>56</b> |

| 5.7.1 Register Access                           | 57        |

| 5.7.2 SCC Interrupts                            | 57        |

| 5.8 Peripheral Device DMA Controller            | <b>58</b> |

| 5.8.1 MAR/TCR Memory Locations                  | <b>59</b> |

| 5.8.2 DMA Terminal Count Interrupts             | <b>59</b> |

| 5.8.3 I/O DMA Command Register                  | <b>60</b> |

| 5.9 VMEbus Slave Interface                      | <b>60</b> |

| 5.9.1 VMEbus Slave Address Decoder              | <b>62</b> |

| 5.9.2 VMEbus Mailboxes and Software Reset       | 62        |

| 5.9.3 Mailbox Slave Address Decoder             | <b>63</b> |

| 5.9.4 Configuring the Mailbox Interrupts        | 63        |

| 5.9.5 Software Reset.                           | <b>64</b> |

| 5.10 VMEbus Interrupter                         | <b>64</b> |

| 5.11 VMEbus Master Interface                    | 65        |

| 5.12 Operating Controls and Indicators          | <b>68</b> |

| 5.12.1 Fault Indicator.                         | <b>68</b> |

| 5.12.2 I/O DMA Indicator                        | <b>68</b> |

| 5.12.3 VME Access Indicator                     | <b>68</b> |

| 5.13 Serial EEPROM Operation                    | <b>68</b> |

| 5.14 Boa        | rd Select Switches                                             |

|-----------------|----------------------------------------------------------------|

| 6 Diagno        | stics 73                                                       |

| 6.1 Test        | s Performed                                                    |

| 6.1.1           | ROM Checksum                                                   |

| 6.1.2           | Dynamic RAM (DRAM)                                             |

| 6.1.3           | 68901 Multi-function Peripheral (MFP)                          |

| 6.1.4           | VMEbus Slave Interface (VSI)                                   |

| 6.1.5           | EEPROM                                                         |

| 6.1.6           | DMA Controller                                                 |

| 7 Boot Lo       | pad Procedure 72                                               |

| 7.1 Dov         | vnload Message Format                                          |

|                 | vnload Procedure                                               |

| A 16-port       | EIA-232 Electrical Interface Module 83                         |

| A.1 Mo          | dem Clocks                                                     |

| A.1.1           | Receive Clock Inputs    83                                     |

| A.1.2           | Transmit Clock Inputs/Outputs    83                            |

| A.2 Z85         | C30 or Z85230 Serial Communications Controller                 |

| A.2.1           | SCC Register Access                                            |

| A.2.2           | SCC Timebase                                                   |

| A.2.3           |                                                                |

| A.3 Mo          | dem Control                                                    |

| A.3.1           | Data Set Ready    86                                           |

| A.3.2           | Clear To Send.         87                                      |

| A.3.3           | Data Carrier Detect.    82                                     |

| A.3.4           | Data Terminal Ready    87                                      |

| A.3.5           | Request To Send    82                                          |

| A.4 Cor         | nnector Pin Assignments                                        |

| <b>B</b> 8-port | MIL-STD-188C and 8-port EIA-232 Electrical Interface Module 93 |

| B.1 Mo          | dem Clocks                                                     |

| B.1.1           | Receive Clock Inputs                                           |

| B.1.2           | Transmit Clock Inputs and Outputs.    93                       |

| B.2 Z83                                                                                                                              | 5C30 or Z85230 Serial Communications Controller                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B.2.1                                                                                                                                | SCC Register Access                                                                                                                                                                                                                                                                                                |

| B.2.2                                                                                                                                | SCC Timebase                                                                                                                                                                                                                                                                                                       |

| B.2.3                                                                                                                                | SCC DMA                                                                                                                                                                                                                                                                                                            |

| B.3 Tra                                                                                                                              | nsmit/Receive Polarity                                                                                                                                                                                                                                                                                             |

| B.4 Dri                                                                                                                              | ver Supply Voltages                                                                                                                                                                                                                                                                                                |

| B.5 Inte                                                                                                                             | erface Driver Waveshaping                                                                                                                                                                                                                                                                                          |

| B.6 Inte                                                                                                                             | erface Receiver Response Control                                                                                                                                                                                                                                                                                   |

| B.7 Mo                                                                                                                               | dem Control                                                                                                                                                                                                                                                                                                        |

| <b>B.7.1</b>                                                                                                                         | Data Set Ready    98                                                                                                                                                                                                                                                                                               |

| B.7.2                                                                                                                                | Clear To Send                                                                                                                                                                                                                                                                                                      |

| B.7.3                                                                                                                                | Data Carrier Detect    99                                                                                                                                                                                                                                                                                          |

| B.7.4                                                                                                                                | Data Terminal Ready                                                                                                                                                                                                                                                                                                |

| B.7.5                                                                                                                                | Request To Send                                                                                                                                                                                                                                                                                                    |

| <b>B.8</b> Co                                                                                                                        | nnector Pin Assignments                                                                                                                                                                                                                                                                                            |

|                                                                                                                                      |                                                                                                                                                                                                                                                                                                                    |

| C 8-port                                                                                                                             | V.35 CCITT Electrical Interface Module 103                                                                                                                                                                                                                                                                         |

|                                                                                                                                      |                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                      | dem Clocks                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                      |                                                                                                                                                                                                                                                                                                                    |

| C.1 Mo                                                                                                                               | dem Clocks                                                                                                                                                                                                                                                                                                         |

| C.1 Mo<br>C.1.1<br>C.1.2                                                                                                             | dem Clocks                                                                                                                                                                                                                                                                                                         |

| C.1 Mo<br>C.1.1<br>C.1.2                                                                                                             | dem Clocks103Receive Clock Inputs103Transmit Clock Inputs and Outputs103                                                                                                                                                                                                                                           |

| C.1 Mo<br>C.1.1<br>C.1.2<br>C.2 Z85                                                                                                  | dem Clocks103Receive Clock Inputs103Transmit Clock Inputs and Outputs103iC30 or Z85230 Serial Communications Controller104                                                                                                                                                                                         |

| C.1 Mo<br>C.1.1<br>C.1.2<br>C.2 Z83<br>C.2.1                                                                                         | dem Clocks103Receive Clock Inputs103Transmit Clock Inputs and Outputs1035C30 or Z85230 Serial Communications Controller104SCC Register Access104                                                                                                                                                                   |

| C.1 Mo<br>C.1.1<br>C.1.2<br>C.2 Z85<br>C.2.1<br>C.2.2<br>C.2.3                                                                       | dem Clocks103Receive Clock Inputs103Transmit Clock Inputs and Outputs103iC30 or Z85230 Serial Communications Controller104SCC Register Access104SCC Timebase106                                                                                                                                                    |

| C.1 Mo<br>C.1.1<br>C.1.2<br>C.2 Z85<br>C.2.1<br>C.2.2<br>C.2.3<br>C.3 Dri                                                            | dem Clocks103Receive Clock Inputs103Transmit Clock Inputs and Outputs1035C30 or Z85230 Serial Communications Controller104SCC Register Access104SCC Timebase106SCC DMA106                                                                                                                                          |

| C.1 Mo<br>C.1.1<br>C.1.2<br>C.2 Z85<br>C.2.1<br>C.2.2<br>C.2.3<br>C.3 Dri<br>C.4 Sin                                                 | dem Clocks103Receive Clock Inputs103Transmit Clock Inputs and Outputs1035C30 or Z85230 Serial Communications Controller104SCC Register Access104SCC Timebase106SCC DMA106ver Supply Voltages106                                                                                                                    |

| C.1 Mo<br>C.1.1<br>C.1.2<br>C.2 Z88<br>C.2.1<br>C.2.2<br>C.2.3<br>C.2.3<br>C.3 Dri<br>C.4 Sin<br>C.5 Dif                             | dem Clocks103Receive Clock Inputs103Transmit Clock Inputs and Outputs1035C30 or Z85230 Serial Communications Controller104SCC Register Access104SCC Timebase106SCC DMA106gle-ended Interface106                                                                                                                    |

| C.1 Mo<br>C.1.1<br>C.1.2<br>C.2 Z88<br>C.2.1<br>C.2.2<br>C.2.3<br>C.2.3<br>C.3 Dri<br>C.4 Sin<br>C.5 Dif                             | dem Clocks103Receive Clock Inputs103Transmit Clock Inputs and Outputs103GC30 or Z85230 Serial Communications Controller104SCC Register Access104SCC Timebase106SCC DMA106ver Supply Voltages106gle-ended Interface106ferential Interface106                                                                        |

| C.1 Mo<br>C.1.1<br>C.1.2<br>C.2 Z88<br>C.2.1<br>C.2.2<br>C.2.3<br>C.3 Dri<br>C.4 Sin<br>C.5 Dif<br>C.6 Mo                            | dem Clocks103Receive Clock Inputs103Transmit Clock Inputs and Outputs1035C30 or Z85230 Serial Communications Controller104SCC Register Access104SCC Timebase106SCC DMA106gle-ended Interface106ferential Interface106dem Control106                                                                                |

| C.1 Mo<br>C.1.1<br>C.1.2<br>C.2 Z83<br>C.2.1<br>C.2.2<br>C.2.3<br>C.2.3<br>C.3 Dri<br>C.4 Sin<br>C.5 Dif<br>C.6 Mo<br>C.6.1          | dem Clocks103Receive Clock Inputs103Transmit Clock Inputs and Outputs103iC30 or Z85230 Serial Communications Controller104SCC Register Access104SCC Timebase106SCC DMA106ver Supply Voltages106gle-ended Interface106ferential Interface106Data Set Ready and Calling Indicator107                                 |

| C.1 Mo<br>C.1.1<br>C.1.2<br>C.2 Z88<br>C.2.1<br>C.2.2<br>C.2.3<br>C.3 Dri<br>C.4 Sin<br>C.5 Dif<br>C.6 Mo<br>C.6.1<br>C.6.2          | dem Clocks103Receive Clock Inputs103Transmit Clock Inputs and Outputs1035C30 or Z85230 Serial Communications Controller104SCC Register Access104SCC Timebase106SCC DMA106scc DMA106gle-ended Interface106ferential Interface106Data Set Ready and Calling Indicator107Clear To Send107                             |

| C.1 Mo<br>C.1.1<br>C.1.2<br>C.2 Z88<br>C.2.1<br>C.2.2<br>C.2.3<br>C.3 Dri<br>C.4 Sin<br>C.5 Dif<br>C.6 Mo<br>C.6.1<br>C.6.2<br>C.6.3 | dem Clocks103Receive Clock Inputs103Transmit Clock Inputs and Outputs103iC30 or Z85230 Serial Communications Controller104SCC Register Access104SCC Timebase106SCC DMA106ver Supply Voltages106gle-ended Interface106ferential Interface106Data Set Ready and Calling Indicator107Received Line Signal Detector107 |

| D 8-port EIA-422 Electrical Interface Module          | 113 |

|-------------------------------------------------------|-----|

| D.1 Modem Clocks.                                     | 113 |

| D.1.1 Receive Clock Inputs                            | 113 |

| D.1.2 Transmit Clock Inputs/Outputs                   | 113 |

| D.2 Z85C30 or Z85230 Serial Communications Controller |     |

| D.2.1 SCC Register Access                             | 116 |

| D.2.2 SCC Timebase                                    | 116 |

| D.2.3 SCC DMA                                         | 116 |

| D.3 Modem Control                                     | 116 |

| D.3.1 Clear To Send                                   | 116 |

| D.3.2 Receiver Ready                                  | 116 |

| D.3.3 Terminal Ready                                  |     |

| D.3.4 Request To Send                                 |     |

| D.4 Connector Pin Assignments                         |     |

#### Index

**123**

ICP6000(X)/ICP9000(X) Hardware Description and Theory of Operation

## List of Figures

| Figure 2–1:  | EEPROM Boot Flag Word    3                                 | 0 |

|--------------|------------------------------------------------------------|---|

| Figure 3–1:  | ICP6000(X)/ICP9000(X) Switch Settings                      | 7 |

| Figure 3–2:  | ICP6000(X) Labeling and Loopback Connections               | 3 |

| Figure 5–1:  | ICP6000(X)/ICP9000(X) Block Diagram                        | 0 |

| Figure 5–2:  | Control Register 0 Use for DMA                             | 0 |

| Figure 5–3:  | I/O DMA Command Register                                   | 1 |

| Figure 5–4:  | Status Register Use for DMA 6                              | 2 |

| Figure 5–5:  | Control Register 0 Use for VMEbus                          | 6 |

| Figure 5–6:  | Control Register 1                                         | 7 |

| Figure 5–7:  | ICP Front Panel Showing Location of LEDs                   | 9 |

| Figure 5–8:  | Control Register 0 Use for FAULT LED                       | 0 |

| Figure 5–9:  | Control Register 0 Use for EEPROM Operation                | 0 |

| Figure 5–10: | Status Register Use for EEPROM Operation    7              | 1 |

| Figure 5–11: | Status Register Use for Board Select Switches              | 2 |

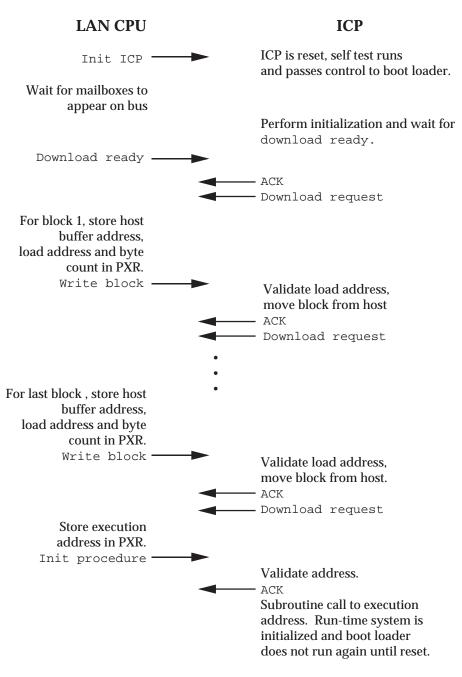

| Figure 7–1:  | Typical Download Sequence    8                             | 1 |

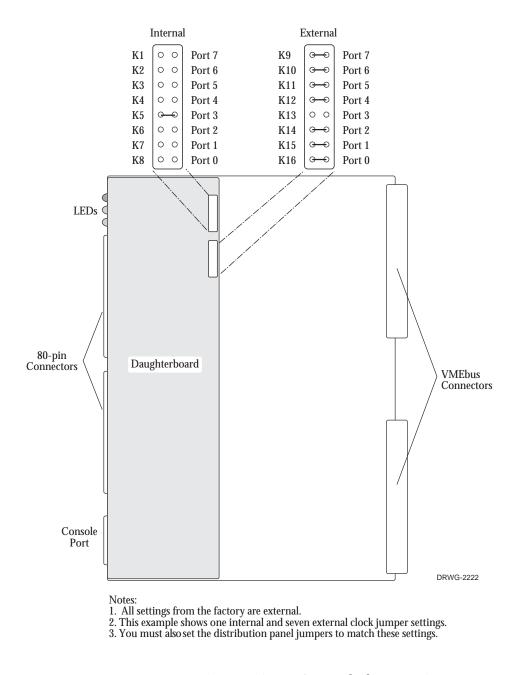

| Figure A-1:  | 16-port EIA-232 Clock Jumper Settings    8                 | 5 |

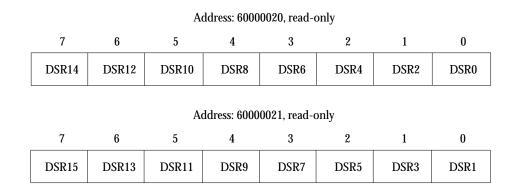

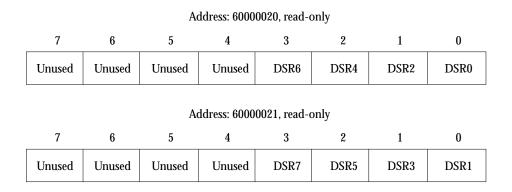

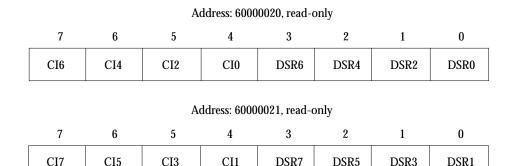

| Figure A-2:  | Data Set Ready Address Decodes    8                        | 7 |

| Figure A–3:  | Data Terminal Ready Address Decodes    8                   | 8 |

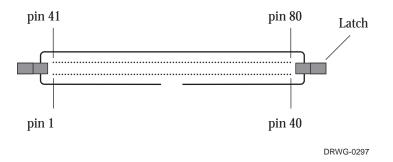

| Figure A-4:  | Front View of 80-pin Connector on the ICP80-pin Connector8 | 8 |

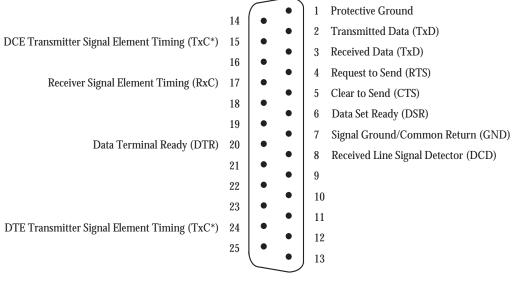

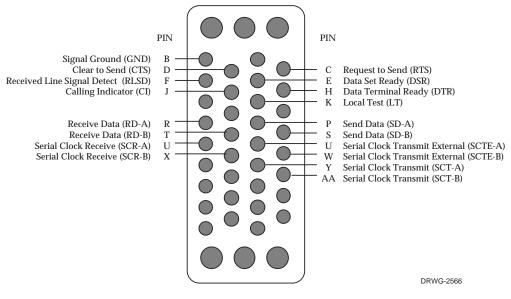

| Figure A–5:  | EIA-232 Interface                                          | 9 |

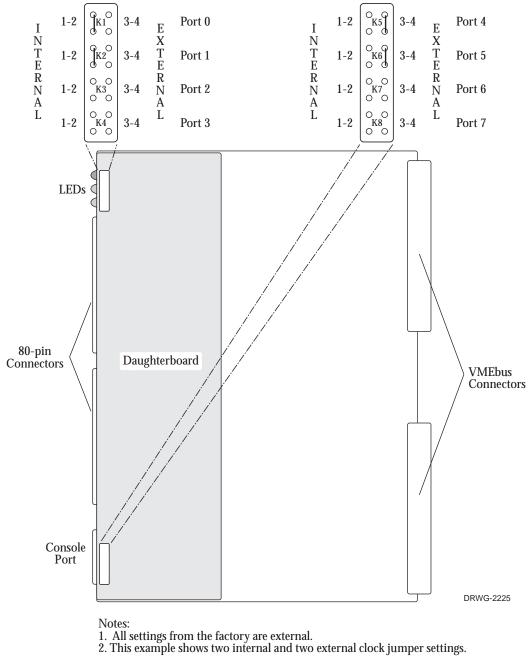

| Figure B-1:  | 8-port MIL-STD-188C or EIA-232 Clock Jumper Settings       | 5 |

| Figure B-2:  | Data Set Ready Address Decodes    10                       | 0 |

| Figure B–3:  | Data Terminal Ready Address Decode.    10                  | 0 |

| Figure B-4:  | EIA-232 or MIL-STD-188C Interface                          | 1 |

| Figure C–1:  | 8-port V.35 Clock Jumper Settings                          | 5 |

|              |                                                            |   |

| Figure C–2: | Data Set Ready and Calling Indicator Address Decodes | 107 |

|-------------|------------------------------------------------------|-----|

| Figure C–3: | Data Terminal Ready and Local Test Address Decodes   | 108 |

| Figure C–4: | V.35 Interface                                       | 109 |

| Figure D–1: | 8-port EIA-422 Clock Jumper Settings                 | 115 |

| Figure D-2: | Terminal Ready Address Decode                        | 117 |

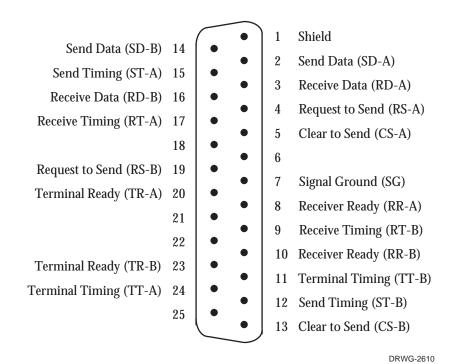

| Figure D–3: | EIA-449 Interface                                    | 118 |

| Figure D-4: | EIA-530 Interface                                    | 119 |

### **List of Tables**

| Table 1–1: | ICP Hardware Features                                              | 18        |

|------------|--------------------------------------------------------------------|-----------|

| Table 2-1: | U39 (ICP6000/ICP9000) Configuration                                | 23        |

| Table 2-2: | U7 (ICP6000X/ICP9000X) Configuration                               | 24        |

| Table 2-3: | U19 (ICP6000/ICP9000) Configuration                                | 25        |

| Table 2-4: | U8 (ICP6000X/ICP9000X) Configuration                               | 27        |

| Table 2–5: | Values for the Slave Address Modifier Compare                      | 31        |

| Table 3–1: | VMEbus Settings                                                    | 38        |

| Table 3–2: | EEPROM Default Values                                              | 41        |

| Table 4–1: | Specifications for ICP Devices                                     | 47        |

| Table 5–1: | General Memory Map                                                 | 51        |

| Table 5–2: | General Interrupt Map                                              | 55        |

| Table 5–3: | Console Port Pin Assignments.                                      | 57        |

| Table 5–4: | MFP DDR Programming                                                | <b>58</b> |

| Table 7–1: | Protocol Exchange Region                                           | 77        |

| Table 7–2: | Protocol Exchange Region for Download Ready Command                | 79        |

| Table A–1: | Clock Jumper Settings for 16-port EIA-232                          | 84        |

| Table A-2: | Pin Assignments for 16-port EIA-232 Cable Connectors               | 90        |

| Table B–1: | Clock Jumper Settings for 8-port MIL-STD-188C or EIA-232           | 94        |

| Table B–2: | Jumper Settings for 8-port MIL-STD-188C                            | 97        |

| Table B–3: | Capacitor Locations for Waveshaping.                               | <b>98</b> |

| Table B–4: | Capacitor Locations for Response Control                           | 99        |

| Table B–5: | Pin Assignments for 8-port MIL-STD-188C & EIA-232 Cable Connectors | 102       |

| Table C–1: | Clock Jumper Settings for 8-port V.35                              | 104       |

| Table C-2: | Pin Assignments for 8-port V.35 Cable Connectors                   | 110       |

| Table D-1: | Clock Jumper Settings for 8-port EIA-422                           | 114       |

DC 900-0408E

Table D-2:

Pin Assignments for 8-port EIA-422 Cable Connectors

120

## Preface

#### **Purpose of Document**

This manual describes Simpact's ICP6000(X)/ICP9000(X) front-end communications processor, its architecture, and how it works in the VMEbus-based system. The information in this manual supplements the basic information that appears in the installation guides delivered with the ICP.

#### **Intended Audience**

This manual should be read by maintenance technicians, computer system integrators, and software developers who need detailed information about the operating theory and features of the ICP hardware.

#### **Organization of Document**

Chapter 1 is a functional overview of the ICP.

Chapter 2 describes how to unpack and configure the ICP.

Chapter 3 describes how to install the ICP.

Chapter 4 defines the mechanical and environmental specifications.

Chapter 5 contains a detailed theory of operation with hardware descriptions.

Chapter 6 describes the hardware self-test diagnostics.

Chapter 7 describes the boot load procedure.

Appendix A describes the daughterboard that provides the 16-port EIA-232 electrical interface.

Appendix B describes the daughterboard that provides the 8-port MIL-STD-188C and EIA-232 electrical interfaces.

Appendix C describes the daughterboard that provides the 8-port V.35 CCITT electrical interface.

Appendix D describes the daughterboard that provides the 8-port EIA-422 electrical interface.

#### References

While reading this manual, you might also need to refer to the manuals listed below:

- *ICP6000/ICP9000 Software Installation Guide for UNIX Products*, Simpact, Inc., DC 900-0550

- MC68020 32-Bit Microprocessor User's Manual, Motorola, Inc.

- MC68030 32-Bit Microprocessor User's Manual, Motorola, Inc.

- MC68901 Multi-function Peripheral Specification, Motorola, Inc.

- *PTBUG Debug and Utility Program Reference Manual*, Simpact, Inc., DC 900-0424

- *VMEbus Specification Manual*, Revision C.1, VMEbus International Trade Association (VITA)

- VSI VMEbus Slave Interface ASIC Manual, Performance Technologies, Inc.

- Z8530 Serial Communications Controller Technical Manual, Zilog, Inc.

- Z85230 Serial Communications Controller Technical Manual, Zilog, Inc.

#### **Document Conventions**

The following conventions apply throughout this document:

- When a specific model number is not mentioned, ICP or ICP6000(X)/ ICP9000(X) refers to all models including the ICP6000X/ICP9000X. The ICP6000 and ICP9000 consist of the same board housed in different form factors.

- A signal name that appears with an overline, for example, ECS, indicates that the signal is asserted low.

- Hexadecimal values are shown preceded by the characters "0x" or with the notation (hex).

- Bits are numbered from right to left, beginning with zero. Bit zero is the low-order bit.

#### **Revision History**

The revision history of the *ICP6000(X)/ICP9000(X)* Hardware Description and Theory of Operation, Simpact document DC 900-0408E, is recorded below:

| <b>Document Revision</b> | <b>Release Date</b> | Description                                                      |

|--------------------------|---------------------|------------------------------------------------------------------|

| DC 900-0408E             | January 1998        | Converted to FrameMaker 5<br>Updated for the high-speed ICP6000X |

#### **Customer Support**

If you are having trouble with any Simpact product, call us at 1-800-275-3889 Monday through Friday between 8 a.m. and 5 p.m. Pacific time.

You can also fax your questions to us at (619) 560-2838 or (619) 560-2837 any time. Please include a cover sheet addressed to "Customer Service."

We are always interested in suggestions for improving our products. You can use the report form in the back of this manual to send us your recommendations.

ICP6000(X)/ICP9000(X) Hardware Description and Theory of Operation

# Chapter

## **Overview of the ICP**

The ICP (intelligent communications processor) is an ancillary computer dedicated to the processing of communications-related data.

The ICP hardware is a single-board computer that has a central processing unit (CPU), random access memory (RAM), programmable read-only memory (PROM), and input/output (I/O) circuitry. The software consists of an onboard operating system, diagnostic tests, host interface drivers, and application routines.

#### 1.1 Purpose of the ICP

The main purpose of the ICP is to improve the overall computing efficiency of the host computer. To do this, low-level communications tasks that are traditionally performed by the host central processor are migrated to the ICP.

An ICP increases overall system bandwidth by distributing the I/O processing away from the host CPU. In the traditional minicomputer architecture, the host services all I/O requests. This load on the CPU has grown steadily as computer peripherals have become increasingly more powerful. Modern operating systems allow intelligent frontend processors to perform these relatively simple tasks. The result is an overall increase in system throughput.

Table 1–1 summarizes the features of the ICP.

| Feature                                                       | Description                                                                                                                                                                                                                                                |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 68020 CPU running at 16 MHz or<br>68030 CPU running at 30 MHz | High-performance processor with linear addressing space                                                                                                                                                                                                    |

| Up to 16 synchronous/asynchronous communications ports        | Serial protocols may be implemented                                                                                                                                                                                                                        |

| 32-channel DMA controller                                     | Full-duplex DMA support provided for all 16 serial com-<br>munications channels; aggregate DMA bandwidth of<br>4.0 megabits/second                                                                                                                         |

| VMEbus master interface                                       | Local processor has direct access to the VMEbus                                                                                                                                                                                                            |

| VMEbus slave interface ASIC                                   | 16-byte dual-ported mailboxes with programmable slave<br>address, programmable interrupt of onboard CPU upon<br>VMEbus access of mailboxes, VMEbus interrupter with<br>programmable level and vector, and reset function initi-<br>ated by VMEbus software |

| EEPROM                                                        | Storage of startup parameters                                                                                                                                                                                                                              |

| EIA-232 console port                                          | Debugging of onboard code using port as console                                                                                                                                                                                                            |

| Two 32-pin JEDEC PROM sockets                                 | Space for power-on diagnostics, debugger, boot loader, and other code                                                                                                                                                                                      |

#### Table 1–1: ICP Hardware Features

#### **1.2 ICP Applications**

The ICP is a general-purpose computer that can do many different tasks. At system startup, the ICP gains its run-time personality from downloaded application software. The application software may be customer-specific or part of a Simpact connectivity product.

The following are some typical applications for the ICP as a front-end processor:

CommunicationsICP-resident software can implement complex communica-<br/>tions protocols, freeing the host for end-user tasks. The pro-<br/>grammable ICP can easily be reconfigured for many serial<br/>protocols, and the software can be modified when protocol<br/>requirements change.

| Multiple Lines   | Multiple communication ports enable the ICP to perform net-<br>work management functions such as message routing, error<br>logging, line-usage monitoring, and various checkout and test-<br>ing functions.     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Acquisition | ICP-resident software can poll remote stations for status mes-<br>sages or maintain a database of alarm-point states. Additional<br>remote stations can be handled easily and economically by add-<br>ing ICPs. |

| Device Control   | The ICP is effective in formatting or modifying large amounts<br>of output data in ways that are inefficient or inappropriate at<br>the host level.                                                             |

ICP6000(X)/ICP9000(X) Hardware Description and Theory of Operation

Chapter

## **2** Unpacking and Configuration

This chapter describes how to unpack and configure an ICP.

#### 2.1 Antistatic Precautions

The ICP circuit board contains integrated circuits that are sensitive to electrostatic discharge (ESD), that is, static electricity. Improper handling can damage the ICP and result in symptoms ranging from unreliable operation to total failure.

#### Caution

Never handle the ICP when it is outside its protective bag without wearing a static-guard wrist strap or taking an equivalent grounding precaution.

Standard ESD handling precautions are sufficient to protect the ICP. If you are not familiar with these techniques, take the following precautions:

- Always work at a static-safe workstation, wearing the static-guard wrist strap provided with each installation kit. Directions for using the wrist strap are on the back of the package.

- Leave the board inside its antistatic plastic bag until you are ready to inspect, configure, or install the board.

- When inspecting or configuring the board, keep the solder side in direct contact with the antistatic bag.

• Return the board to the bag immediately after inspection, configuration, or removal from the host backplane.

#### 2.2 Unpacking the ICP

Inspect the shipping carton for any damage that may have occurred during shipment. If such damage is noted, an agent of the shipping carrier should be present at any further unpacking and contents inspection.

Remove the packing list and check it against the items shipped to ensure that you have received the correct board, cables, and so on.

Carefully remove the board from its antistatic bag and observe normal electrostatic discharge precautions (described in Section 2.1) as you inspect the board for shipping damage.

#### 2.3 Initial Inspection

Use the following procedure when inspecting your board:

- 1. Check overall appearance for breaks or cracks that may have occurred during shipping. If such damage is noted, report it to Simpact, Inc. and *do not proceed* with any further configuration and installation.

- 2. Check for loose or missing hardware such as unseated ICs.

#### 2.4 Configuration

Configuration of the ICP takes place on two levels:

| Jumper Configuration | The jumpers are generally set at the factory, either to a fac- |

|----------------------|----------------------------------------------------------------|

| Options              | tory default or to customer requirements. These options do     |

|                      | not usually require field alteration, but should alteration be |

necessary, full configuration information is provided in Section 2.5.

Software ProgrammableMany of the configuration options normally associatedConfiguration Optionswith jumpers or switches, such as bus request level and<br/>mode, and interrupt request level, are software/firmware<br/>controllable on the ICP. This procedure is described in<br/>Section 2.6.

#### 2.5 Jumper Options

Jumper options are typically installed at the factory to a default specification. They may be changed using the information in the following sections.

#### 2.5.1 U39 (ICP6000/ICP9000) Pinout Configurations

The jumpers at locations K1 and K2 allow for variations in the pinout of PROM/ROM socket, U39 (see Table 2-1). When installing 28-pin devices, be sure that pin 14 of the device enters pin 16 of the socket (bottom justified).

| Device Type             | Jumpers Installed<br>All Other K1, K2 Removed |

|-------------------------|-----------------------------------------------|

| 32Kx8, 28-pin PROM/ROM  | K1-2 to K1-3<br>K2-2 to K2-3                  |

| 64Kx8, 28-pin PROM/ROM  | K1-2 to K1-3<br>K2-1 to K2-2                  |

| 128Kx8, 28-pin PROM/ROM | K2-1 to K2-2                                  |

| 256Kx8, 32-pin PROM/ROM | K1-1 to K1-2<br>K2-1 to K2-2                  |

Table 2-1: U39 (ICP6000/ICP9000) Configuration

#### 2.5.2 U7 (ICP6000X/ICP9000X) Pinout Configurations

The jumpers at locations K1 and K2 allow for variations in the pinout of PROM/ROM socket, U7 (see Table 2-2). When installing 28-pin devices, be sure that pin 14 of the device enters pin 16 of the socket (bottom justified).

| Device Type              | Jumpers Installed<br>All Other K1, K2, K10, K11 Removed |

|--------------------------|---------------------------------------------------------|

| 32Kx8, 28-pin PROM/ROM   | K1-2 to K1-3                                            |

| •                        | K2-2 to K2-3                                            |

|                          | K10-2 to K10-3                                          |

|                          | K11-2 to K11-3                                          |

| 64Kx8, 28-pin PROM/ROM   | K1-2 to K1-3                                            |

| •                        | K2-1 to K2-2                                            |

|                          | K10-2 to K10-3                                          |

|                          | K11-2 to K11-3                                          |

| 128Kx8, 32-pin PROM/ROM  | K1-2 to K1-3                                            |

| Ĩ                        | K2-1 to K2-2                                            |

|                          | K10-2 to K10-3                                          |

|                          | K11-2 to K11-3                                          |

| 256Kx8, 32-pin PROM/ROM  | K1-1 to K1-2                                            |

| -                        | K2-1 to K2-2                                            |

|                          | K10-2 to K10-3                                          |

|                          | K11-2 to K11-3                                          |

| 512Kx8, 32-pin PROM/ROM  | K1-1 to K1-2                                            |

|                          | K2-1 to K2-2                                            |

|                          | K10-1 to K10-2                                          |

|                          | K11-2 to K11-3                                          |

| 1024Kx8, 32-pin PROM/ROM | K1-1 to K1-2                                            |

|                          | K2-1 to K2-2                                            |

|                          | K10-1 to K10-2                                          |

|                          | K11-1 to K11-2                                          |

Table 2-2:

U7 (ICP6000X/ICP9000X)

Configuration

#### 2.5.3 U19 (ICP6000/ICP9000) Pinout Configurations

The jumpers at locations K5, K6, and K7 allow for variation in the pinout of the PROM/ROM/EEPROM/SRAM socket, U19 (see Table 2-3). When installing a 28-pin device, be sure that pin 14 of the device enters pin 16 of the socket (bottom justified). EEPROMs used in this application must have write protection built in.

| Device Type               | Jumpers Installed<br>All Other K5, K6, K7 Removed |

|---------------------------|---------------------------------------------------|

| 8Kx8, 28-pin EEPROM/SRAM  | K6-1 to K6-2<br>K7-1 to K7-2                      |

| 32Kx8, 28-pin EEPROM/SRAM | K5-2 to K5-3<br>K6-1 to K6-2<br>K7-2 to K7-3      |

| 64Kx8, 28-pin PROM/ROM    | K5-1 to K5-2<br>K6-2 to K6-3<br>K7-2 to K7-3      |

| 128Kx8, 32-pin PROM/ROM   | K5-1 to K5-2<br>K6-2 to K6-3                      |

| 256Kx8, 32-pin PROM/ROM   | K5-1 to K5-2<br>K6-2 to K6-3<br>K7-1 to K7-2      |

| tion |

|------|

|      |

#### 2.5.4 U8 (ICP6000X/ICP9000X) Pinout Configurations

The jumpers at locations K5, K6, and K7 allow for variation in the pinout of the PROM/ROM/EEPROM/SRAM socket, U8 (see Table 2-4). When installing a 28-pin device, be sure that pin 14 of the device enters pin 16 of the socket (bottom justified). EEPROMs used in this application must have write protection built in.

| Device Type               | Jumpers Installed<br>All Other K5, K6, K7, K8, K9<br>Removed                 |

|---------------------------|------------------------------------------------------------------------------|

| 8Kx8, 28-pin EEPROM/SRAM  | K6-1 to K6-2<br>K7-2 to K7-3                                                 |

| 32Kx8, 28-pin EEPROM/SRAM | K5-2 to K5-3<br>K6-1 to K6-2<br>K7-2 to K7-3                                 |

| 64Kx8, 28-pin PROM/ROM    | K5-1 to K5-2<br>K6-2 to K6-3<br>K7-2 to K7-3<br>K8-2 to K8-3<br>K9-2 to K9-3 |

| 128Kx8, 32-pin PROM/ROM   | K5-1 to K5-2<br>K6-2 to K6-3<br>K7-2 to K7-3<br>K8-2 to K8-3<br>K9-2 to K9-3 |

| 256Kx8, 32-pin PROM/ROM   | K5-1 to K5-2<br>K6-2 to K6-3<br>K7-1 to K7-2<br>K8-2 to K8-3<br>K9-2 to K9-3 |

| 512Kx8, 32-pin PROM/ROM   | K5-1 to K5-2<br>K6-2 to K6-3<br>K7-1 to K7-2<br>K8-1 to K8-2<br>K9-2 to K9-3 |

| 1024Kx8, 32-pin PROM/ROM  | K5-1 to K5-2<br>K6-2 to K6-3<br>K7-1 to K7-2<br>K8-1 to K8-2<br>K9-1 to K9-2 |

#### Table 2-4: U8 (ICP6000X/ICP9000X) Configuration

#### 2.6 Software Programmable Configuration Options

Many of the configuration options normally associated with jumpers or switches are software/firmware controllable on the ICP.

#### 2.6.1 Configuring the Slave Address Decoder

During hardware installation, parameters for configuring the VMEbus slave address decoder may be programmed into the ICP's EEPROM using PTBUG, the ICP's debugging tool. An additional configurable parameter selects diagnostic and boot load options. Some fixed values must be programmed into the EEPROM as well. Once the EEPROM is programmed, the PROM-resident boot loader reads the values from EEPROM and/or the board select switches and uses them to program the slave address decoder each time the ICP is powered-on or reset.

Table 3–2 shows the EEPROM map and recommended values. (The values shown would be a typical configuration for a Sun-3 or Sun-4.) Entries shown with an asterisk are configurable options. All other entries are not configurable and must be programmed into the EEPROM with the values shown.

#### Note

If the board select switches are set to select an ICP number, EEPROM values are updated for consistency.

The configurable parameters in Table 3–2 are:

- boot flags

- slave address compare (high and low words of address)

- mode selection

- slave address modifier compare

- slave address modifier compare don't care

The options for the configurable parameters are described in the following sections. After you have selected a value for each of these parameters, follow the installation steps in Chapter 3 to program the EEPROM.

#### 2.6.1.1 Boot Flags

The boot flags word determines the operations performed by the PROM-resident firmware when the ICP is powered-on or reset. The PROM code includes a set of diagnostic self-tests that may be enabled or disabled (see Chapter 6). If enabled, errors encountered during the tests may be displayed on a terminal attached to the console port.

The PROM code also includes a boot loader that allows code and data to be downloaded from the host system (see Chapter 7). On completion of the diagnostics (or immediately after reset if diagnostics are disabled), control is normally transferred to the boot loader. If this function is disabled, control is transferred to PTBUG instead, and the PTBUG "boot" command must be used to execute the boot loader.

The five low-order bits of the boot flag word are used to configure these options, as shown in Figure 2-1. The remaining bits are unused.

#### 2.6.1.2 Slave Address Compare

Addresses 0x2E and 0x30 in the EEPROM specify the base VME address where the mailboxes reside. The default of 0xFE000000 assumes A32 addressing. This address can be changed as required for a given environment and must be changed if more than one ICP exists in the chassis. (Each ICP must have a different base address.) The base address of the mailboxes must be on a 512-byte boundary.

#### ICP6000(X)/ICP9000(X) Hardware Description and Theory of Operation

| 15–5       | 4  | 3  | 2       | 1     | 0    |

|------------|----|----|---------|-------|------|

| (not used) | M1 | M0 | DISPLAY | DIAGS | BOOT |

| Mnemonic | Name                     | Description                                                                                                                                                          |

|----------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOT     | Boot Load Execution      | This bit selects the conditions under which<br>the boot loader will execute.<br>0 = boot on power-up or reset<br>1 = boot on PTBUG boot command only                 |

| DIAGS    | Diagnostic Execution     | This bit selects whether or not the diagnostic<br>self-tests will execute on power-up and reset.<br>0 = no diagnostics<br>1 = diagnostics enabled                    |

| DISPLAY  | Diagnostic Error Display | This bit enables or disables the display of<br>diagnostic errors (if any) on the console ter-<br>minal.<br>0 = no output to console<br>1 = display errors on console |

| M1/M0    | DRAM Memory Size         | These bits enable the message size.<br>$0\ 0 = 1$ megabyte<br>$0\ 1 = 4$ megabytes<br>$1\ 0 = 8$ megabytes                                                           |

Figure 2–1: EEPROM Boot Flag Word

#### 2.6.1.3 Mode Selection

The value stored in EEPROM address 0x32 selects whether the ICP will be an A32, A24, or A16 slave. Legal values for this word are as follows:

| A32 slave | 0x04 |

|-----------|------|

| A24 slave | 0x14 |

| A16 slave | 0x34 |

#### 2.6.1.4 Slave Address Modifier Compare

The value stored in EEPROM address 0x34 specifies the address modifier pattern for slave address compares. Table 2–5 lists the legal values for this byte.

| Hex Code   | Function                                   |

|------------|--------------------------------------------|

| 3F         | A24 Standard Supervisory Block Transfer    |

| 3E         | A24 Standard Supervisory Program Access    |

| 3D         | A24 Standard Supervisory Data Access       |

| 3B         | A24 Standard Non-Privileged Block Transfer |

| 3A         | A24 Standard Non-Privileged Program Access |

| 39         | A24 Standard Non-Privileged Data Access    |

| 30         | A24 Don't care about lower four bits       |

|            |                                            |

| 2D         | A16 Short Supervisory Access               |

| 29         | A16 Short Non-Privileged Access            |

| 20         | A16 Don't care about lower four bits       |

|            |                                            |

| 0F         | A32 Standard Supervisory Block Transfer    |

| <b>0</b> E | A32 Standard Supervisory Program Access    |

| 0D         | A32 Standard Supervisory Data Access       |

| 0B         | A32 Standard Non-Privileged Block Transfer |

| 0A         | A32 Standard Non-Privileged Program Access |

| 09         | A32 Standard Non-Privileged Data Access    |

| 00         | A32 Don't care about lower four bits       |

Table 2–5:

Values for the Slave Address Modifier Compare

#### 2.6.1.5 Slave Address Modifier Compare Don't Care

Any or all of the address modifier bits can be ignored in the comparison. The value stored in location 0x36 in the EEPROM specifies a comparison mask where a one in the bit pattern signifies "don't care."

#### 2.6.2 Configuring the VMEbus Master Interface and Interrupter

The ICP allows the local processor to have direct access to the VMEbus through the VMEbus master interface. In addition, the VMEbus interrupter enables the ICP to generate VMEbus interrupts at a given level and vector. Configuration of the VMEbus master interface and interrupter is accomplished each time the ICP is reset, when the host driver passes the relevant parameters to the ICP's boot loader as the first step of the download procedure (described in Chapter 7).

The following 8-bit external variable arrays must be defined by the user during driver installation. One element in each array must be initialized for each ICP configured into the host system:

| icp_vector  | This variable is the vector number to be supplied to the VMEbus as part of the interrupt process.                                                                                                                                                                                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| icp_level   | This variable is the interrupt request level at which the inter-<br>rupt will be generated by the ICP.                                                                                                                                                                                                                                                                                  |

| icp_request | A portion of this variable specifies the VMEbus request mode<br>and the VMEbus bus request level. This value is bit-encoded<br>and must take the form " <i>xxx</i> 10001," where <i>xxx</i> are the user-<br>programmable bits for VMERMS, VMEBR1, and VMEBR0.<br>Refer to Section 5.11 on page 65. The recommended value for<br>this variable is 0xF1.                                 |

| icp_options | This variable specifies the data size and address parameters for<br>VMEbus master mode data transfers. This value is bit-encoded<br>and all bits are user-selectable. Refer to Section 5.11 on page 65<br>for the selection of these eight bits, which are stored into Con-<br>trol Register 1 by the boot loader. For A32/D32 operation, this<br>variable's recommended value is 0x8D. |

After selecting the appropriate values for these variables, refer to the driver installation instructions for your host system in the appropriate ICP software installation guide. These instructions will tell you how to define and initialize the variables. The host driver uses these values to configure the VMEbus master interface and interrupter each time the host system is powered up.

ICP6000(X)/ICP9000(X) Hardware Description and Theory of Operation

## Chapter 3

### **VMEbus Installation**

This chapter describes how to install an ICP. During installation you will perform the following steps:

- Set the board select switches and jumpers

- Plug in the console cable and ICP

- Check and set the EEPROM

- Attach the cables to the upper and lower ports

- Verify the hardware and software installation

You should perform the software installation described in the *ICP6000/ICP9000 Software Installation Guide for UNIX Products* before proceeding with the following hardware installation steps. This avoids extra power-up and power-down cycles.

#### Step 1:

Turn off the power to the host system.

#### Caution

The ICP should never be inserted into or removed from the VMEbus cardcage while power is applied. Insertion or removal with power applied could seriously damage the system or the ICP components.

#### Step 2:

Refer to the documentation provided with your host system for instructions on installing boards in the VMEbus cardcage. This documentation should explain how to access and set the "daisy-chain" backplane jumpers, IACK and Bus Grant. Other preparations, such as setting jumpers on the system's CPU board, may also be required.

#### Note

If the host system's daisy-chain backplane jumpers are not set correctly, the system or the ICP will not operate.

#### Step 3:

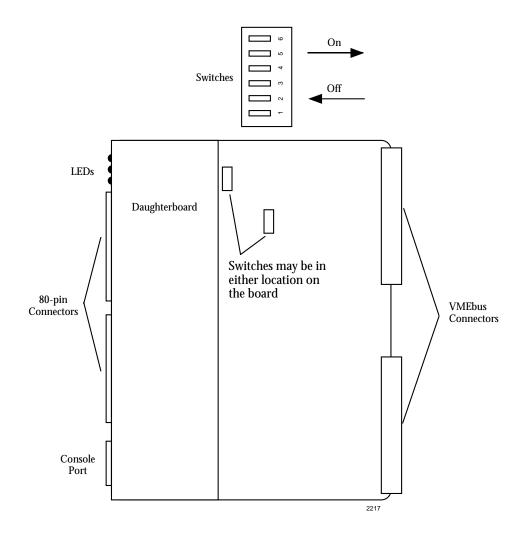

Set the board select switches to the desired position as defined by the required ICP address. Figure 3–1 shows where the switches are on the ICP. Table 3–1 shows the valid settings for the switches and the VMEbus address configured for each.

#### Note

An easy way to remember the orientation of the board select switches is: For debug, set all switches "ON" (toward the console port); for host mode, set all switches "OFF" (toward the VMEbus).

#### Step 4:

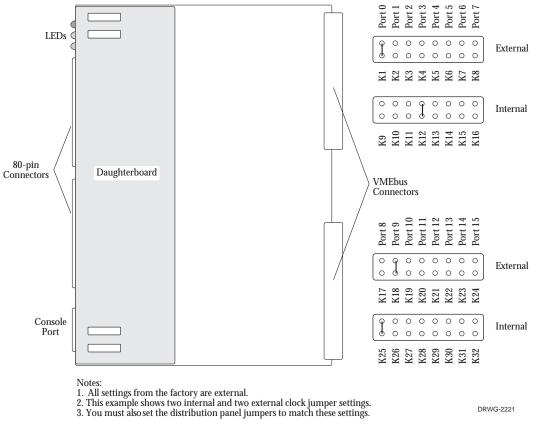

The jumpers from the factory are set for internal clocking. Refer to the appropriate appendix for your electrical interface for figures showing the jumper locations on the ICP.

Figure 3–1: ICP6000(X)/ICP9000(X) Switch Settings

| ICP <sup>a</sup> | Base Address<br>Select |     |     |     |     |     |                                                                               |

|------------------|------------------------|-----|-----|-----|-----|-----|-------------------------------------------------------------------------------|

| Number           | SW6                    | SW5 | SW4 | SW3 | SW2 | SW1 | VMEbus Slave Address                                                          |

| ICPx             | 0                      | 0   | X   | X   | X   | X   | Go to PTBUG                                                                   |

| ICP0             | 1                      | 0   | 0   | 0   | 0   | 1   | F2000000                                                                      |

| ICP1             | 1                      | 0   | 0   | 0   | 1   | 0   | F400000                                                                       |

| ICP2             | 1                      | 0   | 0   | 0   | 1   | 1   | F600000                                                                       |

| ICP3             | 1                      | 0   | 0   | 1   | 0   | 0   | F8000000                                                                      |

| ICP4             | 1                      | 0   | 0   | 1   | 0   | 1   | FA000000                                                                      |

| ICP5             | 1                      | 0   | 0   | 1   | 1   | 0   | FC000000                                                                      |

| ICP6             | 1                      | 0   | 0   | 1   | 1   | 1   | FE000000                                                                      |

| ICP7             | 1                      | 0   | 0   | 0   | 0   | 0   | F0000000                                                                      |

| ICP8             | 0                      | 1   | 0   | 0   | 0   | 0   | FE000000                                                                      |

| ICP9             | 0                      | 1   | 0   | 0   | 0   | 1   | FE000200                                                                      |

| ICP10            | 0                      | 1   | 0   | 0   | 1   | 0   | FE000400                                                                      |

| ICP11            | 0                      | 1   | 0   | 0   | 1   | 1   | FE000600                                                                      |

| ICP12            | 0                      | 1   | 0   | 1   | 0   | 0   | FE000800                                                                      |

| ICP13            | 0                      | 1   | 0   | 1   | 0   | 1   | FE000A00                                                                      |

| ICP14            | 0                      | 1   | 0   | 1   | 1   | 0   | FE000C00                                                                      |

| ICP15            | 0                      | 1   | 0   | 1   | 1   | 1   | FE000E00                                                                      |

| ICP16            | 0                      | 1   | 1   | 0   | 0   | 0   | FE001000                                                                      |

| ICP17            | 0                      | 1   | 1   | 0   | 0   | 1   | FE001200                                                                      |

| ICP18            | 0                      | 1   | 1   | 0   | 1   | 0   | FE001400                                                                      |

| ICP19            | 0                      | 1   | 1   | 0   | 1   | 1   | FE001600                                                                      |

| ICP20            | 0                      | 1   | 1   | 1   | 0   | 0   | FE001800                                                                      |

| ICP21            | 0                      | 1   | 1   | 1   | 0   | 1   | FE001A00                                                                      |

| ICP22            | 0                      | 1   | 1   | 1   | 1   | 0   | FE001C00                                                                      |

| ICP23            | 0                      | 1   | 1   | 1   | 1   | 1   | FE001E00                                                                      |

| ICP <i>x</i>     | 1                      | 1   | X   | X   | X   | X   | Use address, etc. as defined<br>in EE memory and disre-<br>gard board select. |

<sup>a</sup> Note: 0 is off, and 1 is on.

#### Step 5:

Insert the ICP so that the component side is facing the same direction as the other boards in the backplane. If no other boards are in the host's backplane, refer to your system documentation for the correct orientation.

#### **Caution** The ICP will be severely damaged if inserted into the backplane incorrectly.

#### Step 6:

To access PTBUG, connect a terminal to the ICP's console port connector. (See Figure 3–1 on page 37 for the location of the console port.) The terminal should be set to 9600 baud, 8 bits, no parity, one stop bit. For the ICP6000(X) (6U form factor), a console cable is shipped with the board. For the ICP9000(X) (9U form factor), the console cable connects the console port on the ICP board to the corresponding port on the 9U carrier. You will need to provide a null modem (crossover) cable to connect terminal to the console port.

#### Step 7:

Turn on the power to your host system. Type "Control-C" at the terminal to cause the **PTBUG** > prompt to appear on the terminal screen.

Program or verify the EEPROM using the PTBUG "EE" command. The following example verifies that address 0x2E is set to 0xFE00 and sets address 0x7C to 0x8000. Press carriage return to accept the current value; press period to return to the prompt. Because the EEPROM is organized as 64 16-bit words, this command operates in 16-bit word operands. For more information, see the *PTBUG Debug and Utility Program Reference Manual*.

Syntax: PTBUG > ee address Example: PTBUG > ee 2e 0000002E FE00 ? 00000030 0000 ? . PTBUG > ee 7c 0000007C 00B7 ? 8000 00000080 C6A5 ? . PTBUG >

Use this command to program each of the configurable values shown in Table 3–2 into the EEPROM. When programming the configurable parameters (at addresses 0x1C and 0x2E through 0x36), substitute the configurable parameters you selected in Chapter 2 for those shown in the table.

#### Note

During power-up/reset diagnostics, one of the tests calculates a checksum of the ICP' s PROM and compares it to a checksum stored at EEPROM address 0x7C, generating an error if the values do not match. As shown in Table 3–2, EEPROM address 0x7C must initially be programmed to the value 0x8000. This instructs the diagnostic (one time only) to calculate the PROM checksum and store it at this location (overwriting the value 0x8000), rather than do the comparison. Therefore, if you review the contents of EEPROM after you have executed the diagnostics one or more times, address 0x7C will no longer equal 0x8000. This is normal.

| Address<br>(Hex) |   | Description                                       | Value<br>(Hex) |   |

|------------------|---|---------------------------------------------------|----------------|---|

| 0                |   | Validity word                                     | CAFE           |   |

| 2                |   | Validity word                                     | F00D           |   |

| 4-18             |   | Reserved                                          |                |   |

| 1A               |   | Validity word                                     | B0BB           |   |

| 1C               | b | Boot flags <sup>c</sup>                           | 6 or E         |   |

| 1E               |   | Startup code EEPROM address high word             | 0              |   |

| 20               |   | Startup code EEPROM address low word              | C000           |   |

| 22               |   | Address to move startup code to in RAM high word  | 400E           |   |

| 24               |   | Address to move startup code to in RAM low word   | 0              |   |

| 26               |   | Number of bytes of startup code to move high word | 0              |   |

| 28               |   | Number of bytes of startup code to move low word  | 600            |   |

| 2A               |   | Startup code execution address high word          | 400E           |   |

| 2C               |   | Startup code execution address low word           | 020A           |   |

| 2E               | b | Slave address compare high word                   | 0000 or FE00   | d |

| 30               | b | Slave address compare low word                    | F600 or 0200   | d |

| 32               | b | Mode selection                                    | 34 or 4        |   |

| 34               | b | Slave address modifier compare                    | 20             |   |

| 36               | b | Slave address modifier don't care                 | F              |   |

| 38               |   | Master enable                                     | 60             |   |

| 3A-7E            |   | Reserved                                          |                |   |

#### Table 3–2: EEPROM Default Values

<sup>a</sup> PTBUG is used to verify these values.

<sup>b</sup> Entries shown with a "b" are configurable options.

<sup>c</sup> See Figure 2–1 on page 30 for further information about the boot flags.

<sup>d</sup> This value is determined by the board select switches shown in Figure 3–1 on page 37.

Step 8:

When EEPROM programming is complete, enter "BO" <CR> to re-enter the download routine.

Step 9:

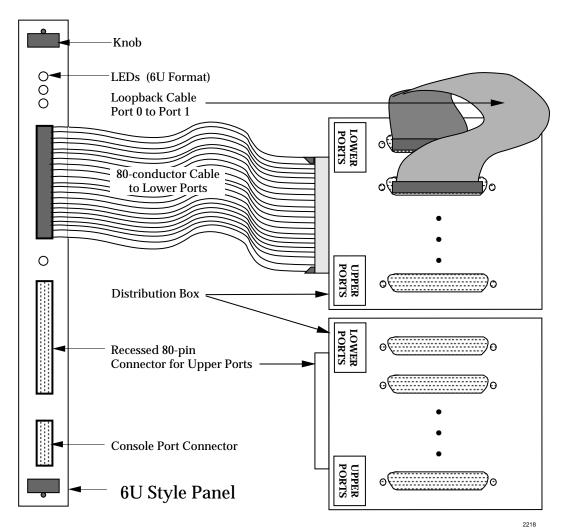

Attach the cables to the upper and lower ports. Install the loopback cable from Port 0 to Port 1 in preparation for verification testing. Refer to Figure 3–2.

#### Step 10:

If you previously performed the software installation to configure the new kernel or boot operating system for Simpact's hardware, power on the system to boot the new kernel or operating system. Otherwise, boot the existing kernel and refer to the *ICP6000/ICP9000 Software Installation Guide for UNIX Products* to perform the software installation.

Step 11:

After you boot the new kernel or operating system, verify the hardware and software installation by running the verification test. Refer to the *ICP6000/ICP9000 Software Installation Guide for UNIX Products*.

Note

Some operating systems support loadable drivers rather than requiring the build of a new image.

Note: Connections for the 9U panel are similar.

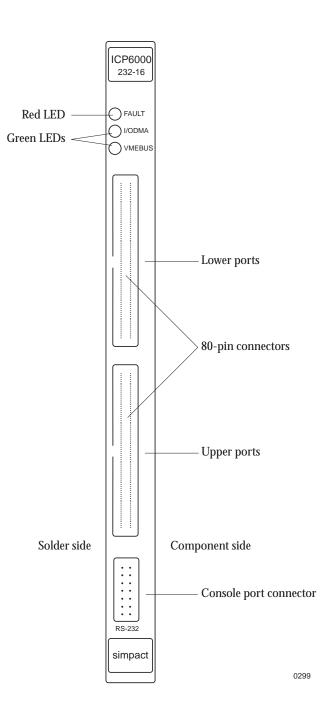

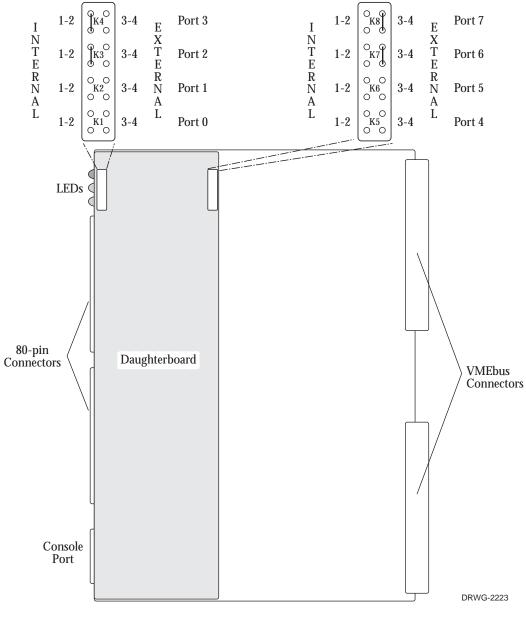

Figure 3–2: ICP6000(X) Labeling and Loopback Connections

# Chapter

## Hardware Specifications

The ICP6000(X)/ICP9000(X) consists of a base board that is a VMEbus controller, an Electrical Interface Module (EIM) daughterboard, and one or more passive distribution panels. The base board contains the 680x0, memory, VMEbus interfaces, and DMA controller. The EIM contains the communications and line interface devices. The distribution panel provides the required transition from the ICP to the connector interface.

#### 4.1 Mechanical and Environmental Specifications

The following sections define the requirements for the ICP.

#### 4.1.1 Physical Characteristics

|             | ICP6000(X) |          | ICP9000(X) |           |

|-------------|------------|----------|------------|-----------|

| Width       | 234 mm     | (9.2 in) | 368 mm     | (14.5 in) |

| Depth       | 160 mm     | (6.3 in) | 403 mm     | (15.9 in) |

| Front Panel | 20.3 mm    | (0.8 in) | 20.3 mm    | (0.8 in)  |

#### 4.1.2 Power Requirements

| +5Vdc +/-5%  | 5.0 amps (typical)  |

|--------------|---------------------|

|              | 6.0 amps (maximum)  |

| +12Vdc +/-5% | 0.15 amps (maximum) |

| -12Vdc +/-5% | 0.15 amps (maximum) |

The host power supply *must* meet these requirements. Be sure to consider the needs of all devices that are serviced by the power supply. Consider both total current for each voltage source and total power.

#### 4.1.3 Environment

Several environmental factors should be considered to ensure reliable operation of the ICP and its host system.

The room air conditioning system should provide cool, filtered, humidified air. Temperature should be held as stable as possible to prevent thermal-related failures. Low humidity contributes to static electricity, which can cause catastrophic failures. The allowable temperature and humidity ranges are as follows:

| Temperature | 0° to 55° C, operating       |

|-------------|------------------------------|

|             | -55° to 85° C, non-operating |

| Humidity    | 10% to 90%, non-condensing   |

Recommended operating conditions are 20 degrees Centigrade (70 degrees Fahrenheit) and 45 percent relative humidity.

#### 4.2 Device Specifications

Table 4–1 lists the specifications for the devices on the base board.

| Device           | Specification                      |                             |  |

|------------------|------------------------------------|-----------------------------|--|

| Processor        | 68020 at 16 MHz or 68030 at 30 MHz |                             |  |

| Main RAM         | 1 or 4 Megabytes Dynamic           |                             |  |

| PROM/EEPROM/SRAM | Two 32-pi                          | Two 32-pin JEDEC Byte Ports |  |

|                  | Socket 1                           | 32Kx8 PROM or               |  |

|                  |                                    | 64Kx8 PROM or               |  |

|                  |                                    | 128Kx8 PROM or              |  |

|                  |                                    | 256Kx8 PROM or              |  |

|                  |                                    | 512Kx8 PROM or              |  |

|                  |                                    | 1024Kx8 PROM                |  |

|                  | Socket 2                           | 8Kx8 EEPROM or              |  |

|                  |                                    | 8Kx8 SRAM or                |  |

|                  |                                    | 32Kx8 EEPROM or             |  |

|                  |                                    | 32Kx8 SRAM or               |  |

|                  |                                    | 64Kx8 PROM or               |  |

|                  |                                    | 128Kx8 PROM or              |  |

|                  |                                    | 256Kx8 PROM or              |  |

|                  |                                    | 512Kx8 PROM or              |  |

|                  |                                    | 1024Kx8 PROM                |  |

| VMEbus Master    | A32/A24:                           | D32/D16                     |  |

|                  | Block Mod                          | de                          |  |

|                  | Unaligned                          | Transfers                   |  |

| VMEbus Slave     | A32/A24/A16 D8(0)                  |                             |  |

| Table 4–1: | Specifications | for | ICP | Devices |

|------------|----------------|-----|-----|---------|

|------------|----------------|-----|-----|---------|

# Chapter 5

### Hardware Overview

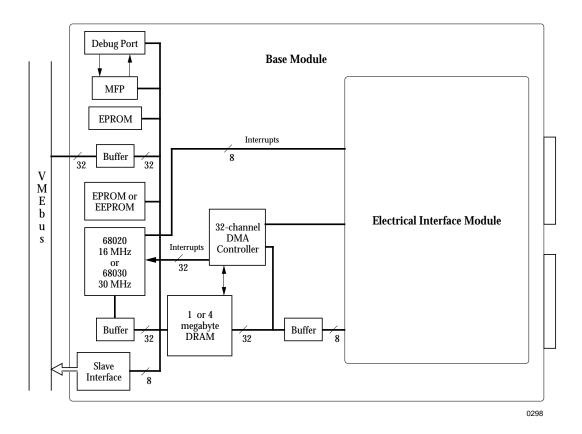

This chapter describes the ICP6000(X)/ICP9000(X) architecture, memory map, buses, and design. Figure 5–1 shows a block diagram of the board, Table 5–1 shows the allocation of memory space, and Table 5–2 shows the interrupt levels, sources, and vectors. All circuitry, pinout, and distribution panel information that applies to specific electrical interfaces, such as EIA-232, EIA-422, and so on is found in Appendix A through Appendix D.

#### 5.1 Internal Architecture

The ICP VMEbus controller allows accesses to the VMEbus that are of indeterminate length and take place without compromising the ability of the I/O DMA controller to transfer data.

Many VMEbus setup parameters usually associated with jumpers or switches are software programmable on the ICP. VMEbus slave address, master request level, and master request mode are programmable by the local processor. An EEPROM is provided for non-volatile storage of these parameters. The board select switches, accessible to the firmware, are provided for those applications that demand a manual input (see Section 5.14).

#### 5.2 Microprocessor

The ICP6000/ICP9000 uses a Motorola 68020 microprocessor running at 16 MHz. The ICP6000X/ICP9000X uses a Motorola 68030 microprocessor running at 30 MHz.

Figure 5–1: ICP6000(X)/ICP9000(X) Block Diagram